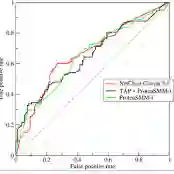

Event-based Cameras (EBCs) are widely utilized in surveillance and autonomous driving applications due to their high speed and low power consumption. Corners are essential low-level features in event-driven computer vision, and novel algorithms utilizing event-based representations, such as Threshold-Ordinal Surface (TOS), have been developed for corner detection. However, the implementation of these algorithms on resource-constrained edge devices is hindered by significant latency, undermining the advantages of EBCs. To address this challenge, a near-memory architecture for efficient TOS updates (NM-TOS) is proposed. This architecture employs a read-write decoupled 8T SRAM cell and optimizes patch update speed through pipelining. Hardware-software co-optimized peripheral circuits and dynamic voltage and frequency scaling (DVFS) enable power and latency reductions. Compared to traditional digital implementations, our architecture reduces latency/energy by 24.7x/1.2x at Vdd = 1.2 V or 1.93x/6.6x at Vdd = 0.6 V based on 65nm CMOS process. Monte Carlo simulations confirm robust circuit operation, demonstrating zero bit error rate at operating voltages above 0.62 V, with only 0.2% at 0.61 V and 2.5% at 0.6 V. Corner detection evaluation using precision-recall area under curve (AUC) metrics reveals minor AUC reductions of 0.027 and 0.015 at 0.6 V for two popular EBC datasets.

翻译:事件相机因其高速与低功耗特性,在监控与自动驾驶领域得到广泛应用。角点作为事件驱动计算机视觉中的关键底层特征,基于事件表示的新型算法(如阈值-序数曲面)已被开发用于角点检测。然而,在资源受限的边缘设备上实现这些算法时,显著延迟阻碍了事件相机的优势发挥。为应对这一挑战,本文提出一种用于高效TOS更新的近存储器架构(NM-TOS)。该架构采用读写解耦的8T SRAM单元,并通过流水线优化图像块更新速度。经软硬件协同优化的外围电路及动态电压频率缩放技术,实现了功耗与延迟的降低。基于65纳米CMOS工艺,与传统数字实现方案相比,本架构在Vdd=1.2V时延迟/能耗降低24.7倍/1.2倍,在Vdd=0.6V时降低1.93倍/6.6倍。蒙特卡洛仿真验证了电路的稳健性:工作电压高于0.62V时误码率为零,0.61V时仅0.2%,0.6V时为2.5%。采用精确率-召回率曲线下面积指标进行角点检测评估显示,在两个常用事件相机数据集上,0.6V电压下的AUC值仅分别下降0.027与0.015。