StarryHeavensAbove文章导读

伴随AI热潮,AI芯片备受关注

首先,下面两篇文章对AI芯片的大环境做了一些讨论:

2017年,AI芯片是半导体产业的亮点,而它受到的关注又远远超出半导体的圈子。这一年,从科技巨头到初创公司,新老角色轮番登场,为我们上演了精彩好戏。若干年后,当我们再回头来看,一定可以把2017年作为AI芯片元年。

中国初创公司在AI芯片(IP)领域的机会:一家之言,主要是对市场的讨论

去年11月的时候第一次思考这个题目,今年3月做过一次更新。短短几个月,AI芯片领域变化不断,新闻不断,有必要再更新一下这个讨论。希望这次能把一个更为完整的分析呈现给大家。

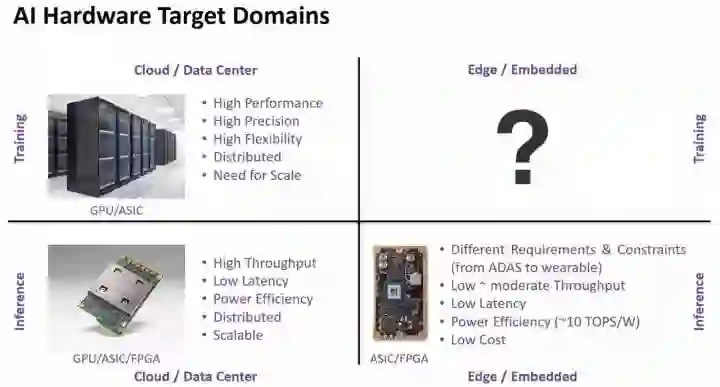

具体来讲,AI/ML/DL的硬件大体上可以按照下图的4个象限进行分类。

从功能来看,可以分成Training和Inference;而从应用场景则可以分成“ Cloud / Data Center”和“Edge / Embedded”两大类。其中在Edge端做training目前还不是很明确的需求,暂时不去考虑。其它几个象限都有自身实现的需求和约束。为了适应AI应用的需求,大家对于AI硬件做了大量的探索,具体可以参考下面两篇文章:

深度神经网络的模型·硬件联合优化:列举了神经网络硬件实现的各种优化思路

最近,设计“Eyeriss” DCNN加速器的团队发表了一篇综述性文章“Efficient Processing of Deep Neural Networks: A Tutorial and Survey”[1],涉及神经网络很多内容,对神经网络感兴趣的同学可以好好看看。这个团队对各种Inference加速的思路做了深入分析,我想和大家重点看看DNN模型和硬件的联合优化。

AI会给芯片设计带来什么?:讨论在AI需求的牵引下,哪些芯片设计技术会受到影响

前段时间和朋友交流,我说从现在开始AI会是芯片技术进步的主要推动力。他问具体体现在什么方面,我说“方法,架构,实现和工具都会有吧”。后来我一直也在考虑这个问题,似乎可以更全面的回答一下。不过,讨论这么大的话题我也没什么把握,说的不对的,讲的不清的,或者说漏了的,请大家多指教。

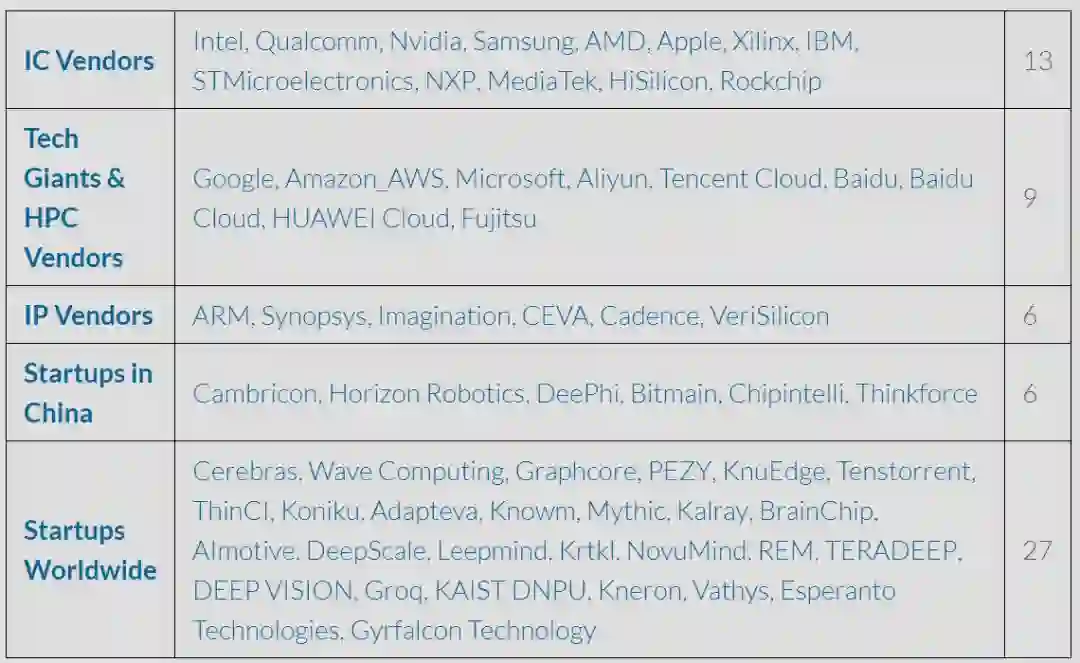

这些技术上的探索逐渐落地,催生了大量的AI处理器设计。为了能比较方便的对比,我在Github上整理了一个AI处理器的列表:Deep-Learning-Processor-List

(basicmi.github.io/Deep-Learning-Processor-List/)

下面的文章从不同的层面介绍AI芯片的相关内容。

•••

对于云端的应用,今年3到5月Nvidia和Google都发布了一些自己的设计,也有一点较劲的意思。如果关注这个故事,可以参考这一系列文章(按照时间顺序):

Google TPU 揭密:对Google TPU论文的初步分析

Google TPU(Tensor Processing Unit)问世之后,大家一直在猜测它的架构和性能。Google的论文“In-Datacenter Performance Analysis of a Tensor Processing Unit”让我们有机会一探究竟。

脉动阵列 - 因Google TPU获得新生:进一步详细分析Google TPU的核心

Google TPU让“脉动阵列”(systolic array)这项“古老”的技术又回到大家的视野当中。短短几天,各种争论不绝于耳。其中有一个评论我比较喜欢,“这次google tpu让像我这样的年轻后辈又有机会能重新认识systolic,也很有意思”。是啊,还是让我们静下心来,重新认识一下“脉动阵列”这位老朋友吧。

Nvidia Volta - 架构看点:分析GTC2017上发布的新GPU Volta架构

Nvidia CEO黄仁勋的GTC主旨演讲凌晨结束,股票大涨,媒体炸锅。同时,http://devblogs.nvidia.com上刊出一篇文章“Inside Volta: The World’s Most Advanced Data Center GPU”,比较详细的介绍了Nvidia最新的Volta架构。这篇文章非常值得一读,推荐大家点击原文链接好好看看。当然你也可以等一等,估计明天就会出现很多对这篇文章的翻译。这里我就不做翻译了,而是想快速和大家分享一下在架构层面我觉得比较重要的地方,供大家参考。

从Nvidia开源深度学习加速器说起:补充分析Nvidia开源Xavier DLA的情况

GTC2017大会,充斥着各种新闻,以至于“XAVIER DLA NOW OPEN SOURCE”这条消息似乎并没有得到太大关注。但在我看来,对于整个芯片产业来说,这个开源事件将会产生深远影响。我先和大家看看这个DLA的架构,然后一起讨论一下硬件开源的问题。

当然,关注硬件加速的玩家还有很多,比如Graphcore的架构就挺有意思。

几个月前注意到Graphcore这个公司,是因为他们的IPU处理器:Intelligence Processing Unit。但除了看到他们一系列非常漂亮的DNN Graph(比如上面这个对于ResNet Conv1的可视化处理)之外,一直没有更详细的信息。在最近的RAAIS会议上,Graphcore的CTO,Simon Knowles做了一个介绍,让我们可以一窥IPU设计背后的一些思考

AI芯片公司Groq由前Google员工创建,核心成员包括Google TPU的主要设计者之一Jonathan Ross。成立以来他们一直比较低调,刚刚才公开了官网。目前官网只有一张照片,但这张照片给出的信息:单芯片,400TOP/s的性能指标,8TOP/s/W的能效指标,可以说是简单粗暴。从这个团队成员和Google TPU的渊源来看,我们不妨拿Google TPU来作为参考分析一下。

大约四个月前,基于Graphcore CTO Simon Knowles的演讲,我和大家讨论了一下它们的IPU,“解密又一个xPU:Graphcore的IPU”。10月底,Simon Knowles又在UC Berkeley做了一个演讲(点击文末阅读原文查看),介绍了IPU的更多细节和Benchmark的结果。

Petascale AI芯片Vathys:靠谱项目?清奇脑洞?还是放卫星?

我之前连续介绍了一下Graphcore和Groq的进展,本来打算开始写全年总结了。没想到年底又冒出一个Startup,Vathys,在Stanford做了一个介绍,题目是“Petascale Deep Learning on a Single Chip”。又把Deep Learning处理器的指标推到了Petascale。这个项目到底靠谱不靠谱我不好评价,不过他们提出的脑洞倒是挺有意思的,还是一起看看吧。

而在云端另一个有意思的应用是FPGA加速,下面这篇文章可一给大家一个基本的参考。

智慧云中的FPGA:通过Microsoft和Amazon的例子看看Cloud FPGA

人工智能大热之前,Cloud或Data Center已经开始使用FPGA做各种加速了。而随着Deep Learning的爆发,这种需求越来越强劲。本文主要讨论Cloud巨头Amazon和Microsoft的FPGA策略。

•••

2017年的ISSCC会议上的Deep Learning Processo专题,大部分工作都可以落在Edge/Embedded inference这个象限。ISSCC论文虽然还不是最终的产品,但已经非常接近实现了,对于希望在Edge端应用里追求高效率的读者,有非常好的的借鉴意义:

14.1 G. Desoli, STMicroelectronics, Cornaredo, Italy, "A 2.9TOPS/W Deep Convolutional Neural Network SoC in FD-SOI 28nm for Intelligent Embedded Systems"

ISSCC2017 Deep-Learning Processors文章学习 (一)

14.2 D. Shin, et al., "DNPU: An 8.1TOPS/W Reconfigurable CNN-RNN Processor for General-Purpose Deep Neural Networks"

ISSCC2017 Deep-Learning Processors文章学习 (二)

14.3 P. N. Whatmough, et al., "A 28nm SoC with a 1.2GHz 568nJ/Prediction Sparse Deep-Neural-Network Engine with >0.1 Timing Error Rate Tolerance for IoT Applications"

ISSCC2017 Deep-Learning Processors文章学习 (四)

14.4 M. Price, et al., "A Scalable Speech Recognizer with Deep-Neural-Network Acoustic Models and Voice-Activated Power Gating"

14.5 B. Moons, et al., "ENVISION: A 0.26-to-10TOPS/W Subword-Parallel Dynamic-Voltage-Accuracy-Frequency-Scalable Convolutional Neural Network Processor in 28nm FDSOI"

ISSCC2017 Deep-Learning Processors文章学习 (三)

14.6 K. Bong, et al., "A 0.62mW Ultra-Low-Power Convolutional-Neural-Network Face-Recognition Processor and a CIS Integrated with Always-On Haar-Like Face Detector"

ISSCC2017 Deep-Learning Processors文章学习 (七)

14.7 S. Bang, et al., "A 288μW Programmable Deep-Learning Processor with 270KB On-Chip Weight Storage Using Non-Uniform Memory Hierarchy for Mobile Intelligence

ISSCC2017 Deep-Learning Processors文章学习 (五)

•••

传统的IP厂商其实很早就开始AI IP的布局,这些IP也是Edge/Embedded侧SoC中重要的选项。所以,我也介绍了一系列IP的方案。最近Imagination也推出了PowerVR Neural Network Accelerator (NNA) IP,不得不感叹这个领域现在发展的太快。

之前谈了不少机器学习处理器的技术内容,也分析过初创公司在这方面的机会,下面换个角度,看看处理器IP厂商的动作:ARM,CEVA,Synopsys,Cadence。这几家公司不像人工智能初创公司那么抢风头,但技术积累和市场能力都很强,看看它们对机器学习的理解和相关方案很有意义。

处理器IP厂商的机器学习方案 - ARM(在刚发了这篇文章之后,ARM推出了DynamIQ)

不管是在软银收购ARM的时候还是今年的MWC会议上,孙正义都大谈人工智能。但从目前的动态看,ARM在AI平台中还是把自己定位为控制处理器。换句话说,ARM短期之内不会推出专门用于AI的处理器核。不过,考虑到ARM在嵌入式芯片中的统治地位、完善的生态和巨大的开发社区,在ARM的CPU/GPU上实现高效的inference是个值得关注的方向。

CEVA作为传统的DSP IP厂商,人工智能是他们重点关注的方向之一。CEVA的方案主要针对视觉应用,是在XM6图像视频处理器的基础上,通过CDNN工具包(包括软件工具和硬件加速器)实现嵌入式的神经网络。XM6基本还是传统的向量处理器架构,兼顾通用的computer vision应用。针对神经网络的设计主要体现在CDNN工具包上。当然,网站的宣传是一回事,最终还是要看它是不是“架构有效,工具好用,价格合理,支持到位”。

Synopsys在对神经网络的支持方面是起步比较早的。它的EV(Embedded Vision)处理器采用了Vision CPU + CNN加速器的方案,架构上和CEVA的XM6的方案类似。所以,大家比拼的重点还是实现细节。另一个看点是处理器IP和Synopsys其它工具/IP配合是否能给出一个更好的方案,包括SoC架构层面和EDA的层面。

Cadence(Tensilica)的Vision P6 DSP是和CEVA,Synopsys机器学习方案竞争的处理器。不过本文更多的讨论Tensilica的可定制处理器(Customizable Processor)的概念,以及指令扩展的方法在实际应用中的问题。

前面分别讨论了一下CEVA,Synopsys,Cadence的DSP,原本没打算聊高通的Hexagon DSP。一方面高通这个DSP是内部使用,并不算是个公开的IP;另外公开资料也比较少,不太好讨论。不过Hexagon DSP虽是高通自用,但按照高通芯片的出货量,这个DSP的市场占有率是很高的,相当重要。同时,这个DSP经过的几代演进,它的设计和trade-off有很多值得思考的地方。

随着VeriSilicon和Cadence相继发布支持AI(神经网络)的DSP IP,加上CEVA和Synopsys,几家主流DSP IP厂商全部粉墨登场。之前的系列文章“处理器IP厂商的机器学习方案”中已经介绍了CEVA和Synopsys的方案。今天看看VeriSilicon和Cadence的方案吧。

•••

自动驾驶,智能汽车,智慧交通也是AI应用的一个重要领域。对这方面的内容,我也做过一点讨论,希望以后能聊聊更多话题。

之前有文章对比过Nvidia和Qualcomm的自动驾驶方案。和Nvidia主要依赖Deep Learning的自动驾驶方案不同,高通更强调通信的作用,特别是5G在未来自动驾驶中的作用,这也反映了两家公司技术基因的差异。最近高通推出了Snapdragon™ Neural Processing Engine (NPE),加强对on-device deep learning的支持,看起来其汽车平台的拼图更加完整了。

一辆越野车正在崎岖的山路上飞驰,坐在副驾驶座上的你惬意的欣赏着窗外秀美的景色。突然一个急弯,汽车优雅的画了一个弧线,你也感到一股强烈的外力。于是,你转过头想提醒一下司机别开的太快。但驾驶座上并没有人,这是一辆自动驾驶汽车。此时,你的心里稍稍有些不安......

从TI“新”的自动驾驶战略说起

(zhuanlan.zhihu.com/p/27529255)

最近看到一篇文章“TI's Shrewd Robo-Car Strategy | EE Times”(一个翻译的版本:一直低调的德州仪器,这一次带来了什么样的自动驾驶战略?),介绍TI在自动驾驶方面的战略。虽然这几年TI很少抢镜,但想当年TI可是DSP的代名词。所以,在看到这个消息之后,我还是立刻跑到TI的网站,想看看他们的新东西。结果这次他们并没有推出新的硬件,而是基于13/14年就推出的TDA2/3(SoC Processor for Advanced Driver Assist Systems (ADAS))。虽然略感失望的,我们还是仔细看看TI对这个平台的“新包装”吧。

•••

在Deep Learning领域,除了硬件架构的优化,软件栈对于实现的性能和效率也起到至关重要的作用,而软件的工作量比硬件也要大很多。未来我会和大家一起多探讨一下这方面的内容。

熟悉编译器的同学应该对上图并不陌生。它就是大名鼎鼎的LLVM的logo。Google Tensorflow XLA (Accelerated Linear Algebra)就使用了LLVM IR(Intermediate Representation)。而它的“竞争对手”,刚刚发布的TVM/NNVM,则是“Tensor IR Stack for Deep Learning Systems”。IR是什么?为什么重要?我们一起来看看。

•••

除了这些针对性比较强的文章,我也做了一些综合性的讨论,看看更多的方向,不同的思路,还有远方。比如:

最近EETimes上有一篇文章“AI Silicon Preps for 2018 Debuts”,非常全面的介绍了和AI芯片相关的各种问题,值得仔细阅读。由于已经有了翻译文章,我只挑一些个人认为比较有意思的内容和大家一起讨论一下。

AI芯片架构的争论真有意义吗?:探讨生态对于AI芯片的重要性

做了这么多年芯片,像AI芯片这样备受关注的情况还是第一次看到。这段时间随着Volta和TPU2的发布,“GPU好还是TPU好”的争论又热了起来,也有很多断言性的结论。这样的争论真的有意义吗?

通过DARPA项目看看芯片世界的“远方”- Architectures

DARPA的ERI(Electronics Resurgence Initiative)电子复兴计划,目标是应对微电子技术领域即将要面对的来自工程技术和经济成本方面的挑战。最近,ERI又增加了6个新的项目,覆盖材料、架构和设计几大方面。材料方面我不懂,所以还是和大家一起看看架构和设计这两个方向吧。虽然这些项目的实施还需要很长时间,但我们至少可以先看看“问题”是什么,大体的解题思路又是什么。

本文先讨论两个架构方向的项目SDH(Software Defined Hardware)和DSSoC(Domain-Specific System on Chip)。

通过DARPA项目看看芯片世界的“远方”- 自动化工具和开源硬件

上篇文章讨论了一下DARPA的ERI电子复兴计划最近新增的两个架构方面的项目(通过DARPA项目看看芯片世界的“远方”- Architectures)。而新增的项目中还有两个设计领域的项目,IDEAS(Intelligent Design of Electronic Assets)和POSH(Posh Open Source Hardware)。和架构项目的大背景类似,这两个项目也是为了在摩尔定律难以继续的情况下,通过提高设计效率的方法降低整体成本,进而支持半导体产业的持续增长。恰逢Nvidia的NVDLA正式开源,我们正好也可以借这个热点讨论一下开源硬件的问题。

HIVE - DARPA资助的新型处理器

(zhuanlan.zhihu.com/p/27350569)

原文链接:DARPA Funds Development of New Type of Processor | EE Times

LAKE WALES,Fla。 - 一种全新的非冯 - 诺伊曼处理器,称为HIVE - Hierarchical Identify Verify Exploit - 正在由DARPA资助,价值8000万美元, 四年半时间。芯片制造商英特尔和高通正在与国家实验室,大学和国防承包商North Grumman一道参与该项目。

今年的Hot Chips会议,AI相关内容占了很大比例(似乎可以考虑把Logo改改了)。微软的BrainWave,百度的XPU,Jeff Dean的Keynote都是这两天媒体上的热点话题。其实,除了这些热点之外,Hot Chips还有不少和AI/ML/DL相关的看点。

•••

最后,是几个基础技术系列文章,算是“镇店之宝”吧。

“专用处理器系列”:

“Benchmark系列”:

面对越来越多的DNN专用处理器设计(芯片和IP),我们很自然的需要解决一个问题“怎样对不同的DNN处理器设计做出公平的比较和评价?”能不能像手机跑分一样也让它们跑个分呢?这实际是个基准测试(Benchmarking)问题。正好最近看到两个在这方面的尝试,一个是MIT Eyeriss团队给出的DNN Processor Benchmarking Metrics;另一个是百度DeepBench项目的更新。我们可以结合这两个项目讨论一下如何给DNN处理器“跑分”。

“2017年10月23日,中国人工智能产业发展联盟(AIIA)总体组组织了人工智能芯片Benchmark研讨会,正式启动人工智能芯片Benchmark项目。”可以看到,随着越来越多的AI芯片走上舞台,如何对它们进行评测和对比越来越受到关注。我之前就通过两篇“给DNN处理器跑个分”的文章对这个问题进行了一些初步的讨论。“BenchIP:Benchmarking Intelligence Processor”这篇论文非常系统和深入的讨论了这个问题,并提出相应的Benchmark Suite和Benchmarking Methodololgy。这里我们就结合这篇论文再谈谈这个话题。

吴博士撰写的“追求极限性能的芯片设计方法系列”:

当今,芯片竞争的核心是性能。尤其在专用处理器和加速器设计领域,性能的互比拼非常激烈,甚至成为国际级别的刷分大赛。通常,国际高水平发物(如ISSCC)会公布出最新的“刷分结果”, 例如图1所示的一个有关CNN加速芯片的性能比拼结果。刷分结果并不代表绝对优势,但也成为设计是否能够被公认为好的设计的一个尺度。但从参考文献中获取的benchmark并不具有完全的可比性,因为每个设计都有自己的特殊之处。本文希望读者能够跳出“互刷分”的思维模式,从极限设计的角度出发,得出理论上尽可能好的设计。

本文首先给出目前性能的评估尺度及关系,之后讲述在这些关系的权衡中,如何采用归一化的尺度将众多指标归结为一个或几个重要的指标,再对这些指标进行极限突破,得到尽可能好的设计。本文仅考虑时序驱动的数字电路,尤其是高性能加速器和专用处理器的设计。而本文的目的就是阐述一个操作性较强的极限量化芯片设计方法。

以及“AI芯片需求分析系列”:

兼容性和灵活度是芯片快速杀入新市场、扩大市场范围、快速适应客户需求,减少开发周期的关键特性。目前深度学习的网络结构已走向了多样化,出现了大量的算法变种、更多的算子和复杂层次结构,这对芯片的支撑灵活度能力提出了挑战。本文通过列举目前图像视频类的典型算法、典型网络结构、典型平台和接口等方面来分析AI芯片的灵活度范围。

目前视频和图像类深度学习加速芯片已经呈现红海状态,而语音类人工智能芯片还处于上升期,文本处理等领域目前还处于探索时期。本文的目的就是从应用和算法的角度分析一下,我们需要一款怎样的语音/文本处理的深度学习芯片?它需要具有怎样的功能覆盖和参数灵活度?这样的芯片能应用到哪些地方?

AI芯片的需求分析是以应用和算法为出发点的,深度学习框架作为算法设计的入口,是非常好的参考。但目前的深度学习框架种类繁多,提供的功能也比较复杂,不利于直接分析硬件需求。相比之下,中间表示层(IR)往往更接近硬件实现,可以认为是软硬件之间的桥梁,对AI芯片的专用指令集设计具有非常高的参考价值。因此,我们不妨从两个中间表示层工具(NNVM和ONNX)出发,通过观察它们的原语操作,思考我们需要在AI芯片中支持什么样的运算算子。

题图来自网络,版权归原作者所有