从晶圆到芯片:无损成像法将降低缺陷率!

导读

最近,德国卡尔斯鲁厄理工学院(KIT)的科学家团队通过无损成像法,获取了晶体内部的三维图像,从而测量晶体内部的位错,为计算机芯片制造工艺的优化提供帮助。

背景

位错,又可称为差排(英文:dislocation)。在材料科学中,指晶体材料的一种内部微观缺陷,即原子的局部不规则排列(晶体学缺陷)。从几何角度看,位错属于一种线缺陷,可视为晶体中已滑移部分与未滑移部分的分界线,其存在对材料的物理性能,尤其是力学性能,具有极大的影响。

“位错”这一概念最早由意大利数学家和物理学家维托·伏尔特拉(Vito Volterra)于1905年提出。为了直观的认识位错这一概念,我们先来看一幅有关晶体位错的透射电镜显微图像。

(图片来源:)

这种线缺陷很大程度地影响着晶体的形变行为,这一数据对于计算机芯片的制造来说也非常重要。在硅晶圆内部,即使存在少量的位错也会导致有缺陷的计算机芯片,因此导致产品报废。

创新

最近,德国卡尔斯鲁厄理工学院(KIT)的科学家团队通过无损成像法,获取了晶体内部的三维图像,从而判断晶体内部的位错。正如《物理评论快报》(Physical Review Letters)杂志所报道的,科学家们将两种X光方法与特种光学显微镜术相结合来实现这一技术。

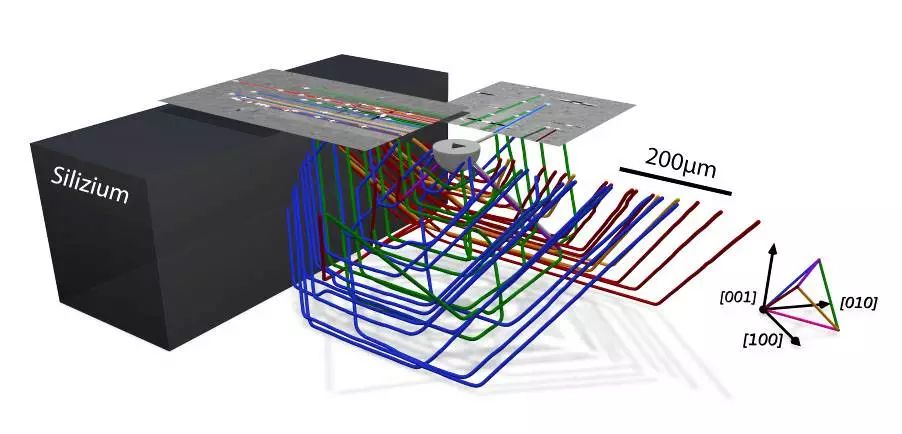

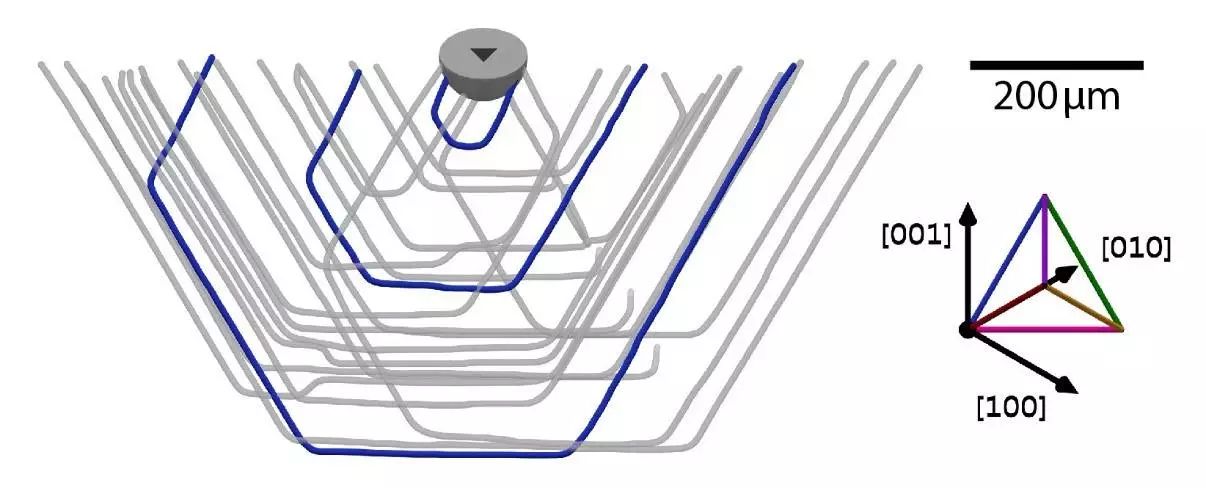

(图片来源:D. Hänschke/KIT)

技术

KIT 光子科学与同步辐射研究所的物理学家 Daniel Hänschke 博士表示,在特殊工艺例如热量的影响下,理解机械表面的微小缺陷是如何传播到晶体深处,显得非常重要。他的团队成功地精准测量位错,研究它们之间如何交互以及外部影响。

科学家们分析了单个表面缺陷如何扩散到一组六边形缺陷线中,同时完全无损的区域也保持在这样一个三维网络的中心。Hänschke 指出,结果产生的集体运动会提高或者降低晶圆另一端的大表面区域的面积,从而形成台阶。这些台阶将会对微结构的制造与功能产生不利影响。

通过数学模型的计算,研究成果将有利于更好理解深层的物理原理。团队的另一成员 Elias Hamann 博士解释道,目前使用的模型主要基于在很小的晶体样本中利用电子显微技术测量到的数据。他们的方法也可以应用于研究大型平面晶体,例如商用晶圆。这是判断初始损伤与最终形成的广泛晶体形变之间的细微关系,这些晶体形变引发的主要问题远远超过起初的缺陷。

(图片来源:D. Hänschke/KIT)

这种新型的测量方法,将KIT KARA 同步设施和位于法国格勒诺布尔的欧洲同步辐射光源(ESRF)同步设施中的X射线技术,与CDIC光学显微镜术相结合。

价值

研究成果将帮助改善预测缺陷形成和缺陷传播的现有模型,从而为计算机芯片制造工艺的优化提供帮助。

在一平方厘米的晶圆表面上排列着的晶体管已达几十亿,且有增加的趋势。即使是在晶体表面和内部存在的最小缺陷,也会引起数千的小型电路失效,以及相应的芯片无法使用。产业界对于未来进一步最小化缺陷率,显示出高度兴趣。

关键字

参考资料

【1】https://www.kit.edu/kit/english/pi_2017_168_wafer-to-chip-x-ray-imaging-for-reduced-defect-rate.php

【2】D. Hänschke, A. Danilewsky, L. Helfen, E. Hamann, T. Baumbach. Correlated Three-Dimensional Imaging of Dislocations: Insights into the Onset of Thermal Slip in Semiconductor Wafers. Physical Review Letters, 2017; 119 (21) DOI: 10.1103/PhysRevLett.119.215504

了解更多前沿技术文章,请点击“阅读原文”。咨询和交流,请联系微信:JohnZh1984。